Inovation

Revolutionizing Large-Area Electronics: Scientists Break Record in Stackable Semiconductor Transistors

Researchers at King Abdullah University of Science and Technology (KAUST) in Saudi Arabia have achieved a groundbreaking milestone in microchip design by developing the first six-stack hybrid CMOS for large-area electronics. This achievement, surpassing any previously reported hybrid CMOS designs with only two stacks, sets a new standard in integration density and efficiency. The breakthrough opens up new possibilities in electronic miniaturization and performance enhancements.

Their research has been published in Nature Electronics.

CMOS microchips are ubiquitous in various electronic devices, from smartphones and TVs to satellites and medical equipment. Hybrid CMOS microchips offer significant advantages for large-area electronics. As electronic miniaturization becomes increasingly important for flexible electronics, smart health devices, and the Internet of Things, current design methodologies are reaching their limits.

Lead researcher Associate Professor Xiaohang Li from KAUST’s Advanced Semiconductor Laboratory explained, “To continue advancing, we must look beyond planar scaling and explore solutions like stacking transistors vertically.”

Traditional microchip fabrication processes involve high temperatures that can damage lower layers as new ones are added. The KAUST team’s innovative approach ensured that no fabrication step exceeded 150°C, with most steps completed at room temperature.

Surface smoothness is crucial for optimal performance, and the team made significant improvements to keep the layers smoother than previous processes. Proper alignment of layers is essential for vertical stacking, and the scientists enhanced the fabrication process to achieve optimal connections.

Postdoctoral researcher Saravanan Yuvaraja, the first author of the research paper, stated, “In microchip design, the goal is to pack more power into less space. By refining multiple fabrication steps, we have laid the groundwork for vertical scaling and significantly increasing functional density beyond current limits.” Contributions to the study were also made by Professor Martin Heeney and Adjunct Professor Thomas Anthopoulos from KAUST.

Citation:

Scientists set a new record by stacking semiconductor transistors for large-area electronics (2025, October 17)

retrieved 17 October 2025

from https://techxplore.com/news/2025-10-scientists-stacking-semiconductor-transistors-large.html

This document is subject to copyright. Apart from any fair dealing for the purpose of private study or research, no

part may be reproduced without the written permission. The content is provided for information purposes only.

-

Facebook5 months ago

Facebook5 months agoEU Takes Action Against Instagram and Facebook for Violating Illegal Content Rules

-

Facebook6 months ago

Facebook6 months agoWarning: Facebook Creators Face Monetization Loss for Stealing and Reposting Videos

-

Facebook6 months ago

Facebook6 months agoFacebook Compliance: ICE-tracking Page Removed After US Government Intervention

-

Facebook4 months ago

Facebook4 months agoFacebook’s New Look: A Blend of Instagram’s Style

-

Facebook4 months ago

Facebook4 months agoFacebook and Instagram to Reduce Personalized Ads for European Users

-

Facebook6 months ago

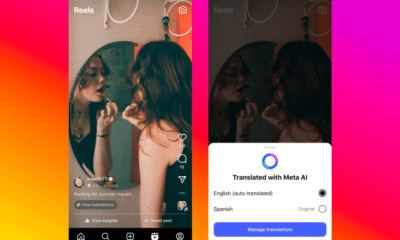

Facebook6 months agoInstaDub: Meta’s AI Translation Tool for Instagram Videos

-

Facebook4 months ago

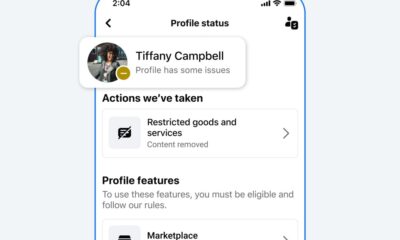

Facebook4 months agoReclaim Your Account: Facebook and Instagram Launch New Hub for Account Recovery

-

Apple5 months ago

Apple5 months agoMeta discontinues Messenger apps for Windows and macOS