AI

Unveiling the Power of Deterministic CPUs in Driving Consistent AI Performance

In the realm of CPU design, speculative execution has been a cornerstone for over three decades. However, with the emergence of speculation in the 1990s, a breakthrough was hailed, akin to previous advancements like pipelining and superscalar execution. Speculation allowed processors to predict branch and memory load outcomes, enabling them to avoid stalls and maintain busy execution units. Despite its benefits, speculation came with drawbacks such as wasted energy, increased complexity, and vulnerabilities like Spectre and Meltdown.

Recently, an alternative to speculative execution has been introduced, revolving around a deterministic, time-based execution model. This new approach challenges the traditional speculative techniques by focusing on a mechanism that is time-based and latency-tolerant. Each instruction is allocated a specific execution slot within the pipeline, ensuring a predictable flow of execution. This new model aims to redefine how modern processors handle latency and concurrency with enhanced efficiency and reliability.

The architecture extends into matrix computation, with a proposal for a RISC-V instruction set under community review. The design includes configurable general matrix multiply (GEMM) units that can support a variety of AI and high-performance computing workloads. This new approach offers scalability comparable to Google’s TPU cores but at a lower cost and power consumption.

Critics may argue that static scheduling introduces latency into instruction execution. However, the time-based approach fills this latency deterministically with useful work, avoiding rollbacks. The new deterministic model ensures a predictable and pre-planned flow of execution, keeping compute resources consistently busy.

One of the key differences with this deterministic model is the elimination of speculation, reducing power consumption and avoiding pipeline flushes. By statically dispatching instructions based on predicted timing, the design simplifies hardware and enhances efficiency. The integration of a time counter and register scoreboard enables deterministic scheduling based on operand readiness and resource availability.

From a programming perspective, the deterministic execution model retains the familiar RISC-V programming model while guaranteeing predictable dispatch and completion times. This deterministic approach simplifies compiler scheduling and reduces reliance on speculative safety nets.

In AI and machine learning workloads, the deterministic model offers steady throughput by issuing vector loads and matrix operations with cycle-accurate timing. This predictability allows for more consistent performance across problem sizes and fewer performance cliffs. The deterministic processors remain fully compatible with mainstream toolchains and programming languages.

Ultimately, the deterministic approach may represent the next architectural leap in CPU design, redefining performance and efficiency. While the future of deterministic CPUs in mainstream computing is yet to be determined, the momentum towards a paradigm shift is evident. Deterministic execution could potentially replace speculation as the next revolution in CPU design.

-

Facebook5 months ago

Facebook5 months agoEU Takes Action Against Instagram and Facebook for Violating Illegal Content Rules

-

Facebook5 months ago

Facebook5 months agoWarning: Facebook Creators Face Monetization Loss for Stealing and Reposting Videos

-

Facebook6 months ago

Facebook6 months agoFacebook Compliance: ICE-tracking Page Removed After US Government Intervention

-

Facebook4 months ago

Facebook4 months agoFacebook’s New Look: A Blend of Instagram’s Style

-

Facebook4 months ago

Facebook4 months agoFacebook and Instagram to Reduce Personalized Ads for European Users

-

Facebook6 months ago

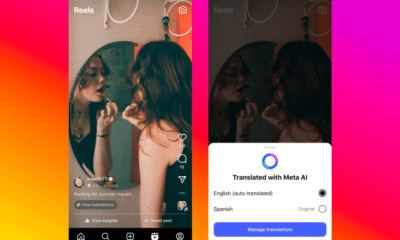

Facebook6 months agoInstaDub: Meta’s AI Translation Tool for Instagram Videos

-

Facebook4 months ago

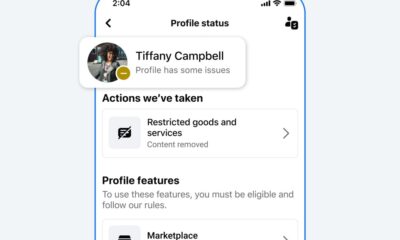

Facebook4 months agoReclaim Your Account: Facebook and Instagram Launch New Hub for Account Recovery

-

Apple5 months ago

Apple5 months agoMeta discontinues Messenger apps for Windows and macOS